Hvorfor bruge Xilinx FPGA XC3S500E-4FTG256I?

Hvis du er elektronikdesigner, kender du måske XC3S500E-4FTG256I -chippen.

Denne Field Programmable Gate Array (FPGA) er meget brugt i forskellige applikationer, fra forbrugerelektronik til industriel kontrol, luftfart, militær og andre områder.

En FPGA er en halvlederenhed, der består af en matrix af konfigurerbare logiske blokke (CLB'er), der er forbundet via programmerbare sammenkoblinger. Brugeren bestemmer disse sammenkoblinger ved at programmere SRAM. En CLB kan være enkel (AND, OR-gate osv.) eller kompleks (en blok RAM). FPGA gør det muligt at foretage ændringer i et design, selv efter at enheden er loddet ind i et printkort.

I denne artikel vil du lære om nogle grundlæggende funktioner i XC3S500E-4FTG256I fra Xilinx og også udforske den professionelle måde at bruge den og dens funktioner på.

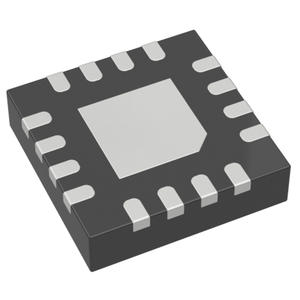

Hvad er XC3S500E-4FTG256I?

XC3S500E-4FTG256I tilhører Spartan-3E FPGA-serien, designet af Xilinx.

Spartan-3E-familien tilbyder en omkostningseffektiv FPGA-løsning med lavt strømforbrug , høj ydeevne og avancerede funktioner på systemniveau.

Xilinx Zynq FPGA

XC3S500E-4FTG256I har 500.000 systemgates, 772 bruger-I/O'er og 36 blok-RAM'er.

Den fungerer ved en maksimal frekvens på 400MHz og har et kernespændingsområde på 1,14V til 1,26V.

XC3S500E-4FTG256I er almindeligt anvendt i applikationer, såsom rumfart og forsvar, bilindustrien, broadcast, forbruger, højtydende databehandling, industriel, medicinsk og videnskabelig, test og måling.

Anmod om original og ny Xilinx XC3S500E-4FTG256I FGPA nu

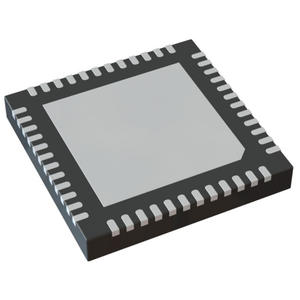

Funktioner i XC3S500E-4FTG256I

• SelectIO-signalering

- Op til 633 I/O-ben

- Atten single-ended signalstandarder

- Otte differentialsignalstandarder inklusive LVDS og RSDS

- Understøttelse af Double Data Rate (DDR)

• Logiske ressourcer

- Rigelige logiske celler med skiftregisterkapacitet

- Brede multipleksere

- Fast look-ahead carry logik

- Dedikerede 18 x 18 multiplikatorer

- JTAG-logik kompatibel med IEEE 1149.1/1532

• SelectRAM hierarkisk hukommelse

- Op til 1.728 Kbits samlet blok RAM

- Op til 432 Kbits samlet distribueret RAM

• Digital Clock Manager (fire DCM'er)

- Eliminering af urskævhed

- Frekvenssyntese

- Faseskift i høj opløsning

English

English Español

Español Português

Português русский

русский français

français 日本語

日本語 Deutsch

Deutsch Tiếng Việt

Tiếng Việt Italiano

Italiano Nederlands

Nederlands ไทย

ไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা

বাংলা Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türk

Türk Gaeilge

Gaeilge عربى

عربى Indonesia

Indonesia norsk

norsk čeština

čeština Ελληνικά

Ελληνικά Українська

Українська Javanese

Javanese فارسی

فارسی български

български ລາວ

ລາວ Latine

Latine Қазақ

Қазақ Euskal

Euskal Azərbaycan

Azərbaycan slovenský

slovenský Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski Српски

Српски 简体中文

简体中文 繁体中文

繁体中文 Беларус

Беларус